12月5日消息,在IEDM 2022(2022 IEEE国际电子器件会议)上,英特尔发布了多项突破性研究成果,继续探索技术创新,以在未来十年内持续推进摩尔定律,最终实现在单个封装中集成一万亿个晶体管。

英特尔的研究人员展示了以下研究成果:3D封装技术的新进展,可将密度再提升10倍;超越RibbonFET,用于2D晶体管微缩的新材料,包括仅三个原子厚的超薄材料;能效和存储的新可能,以实现更高性能的计算;量子计算的新进展。

英特尔技术开发事业部副总裁兼组件研究与设计总经理Gary Patton表示:“自人类发明晶体管75年来,推动摩尔定律的创新在不断满足世界指数级增长的计算需求。

在IEDM 2022,英特尔展示了其前瞻性思维和具体的研究进展,有助于突破当前和未来的瓶颈,满足无限的计算需求,并使摩尔定律在未来继续保持活力。”

此外,为纪念晶体管诞生75周年,英特尔执行副总裁兼技术开发总经理Ann Kelleher博士将于IEDM 2022主持一场全体会议。

届时,Kelleher将概述半导体行业持续创新的路径,即围绕系统级战略联合整个生态系统,以满足世界日益增长的计算需求并以更有效的方式实现创新,从而以摩尔定律的步伐不断前进。

此次会议将于太平洋标准时间12月5日周一上午9点45分(北京时间12月6日周二凌晨1点45分)开始,主题为“庆祝晶体管诞生75周年!摩尔定律创新的演进”。

对满足世界的无限计算需求而言,摩尔定律至关重要,因为数据量的激增和人工智能技术的发展让计算需求在以前所未有的速度增长。

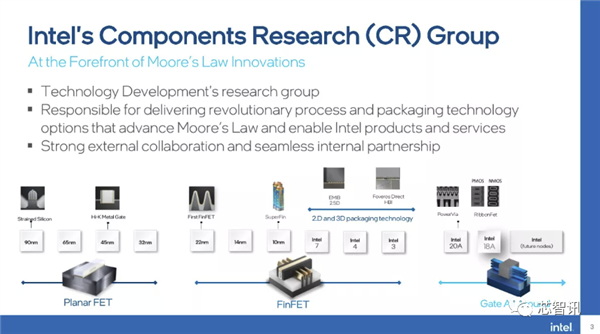

持续创新正是摩尔定律的基石。在过去二十年,许多里程碑式的创新,如应变硅(strained silicon)、Hi-K金属栅极(Hi-K metal gate)和FinFET晶体管,都出自英特尔组件研究团队(Intel’s Components Research Group)。

这些创新在个人电脑、图形处理器和数据中心领域带来了功耗和成本的持续降低和性能的不断增长。

英特尔组件研究团队目前的路线图上包含多项进一步的研究,包括RibbonFET全环绕栅极(GAA)晶体管、PowerVia背面供电技术和EMIB、Foveros Direct等突破性的封装技术。

在IEDM 2022,英特尔的组件研究团队展示了其在三个关键领域的创新进展,以实现摩尔定律的延续:新的3D混合键合(hybrid bonding)封装技术,无缝集成芯粒;超薄2D材料,可在单个芯片上集成更多晶体管;能效和存储的新可能,以实现更高性能的计算。

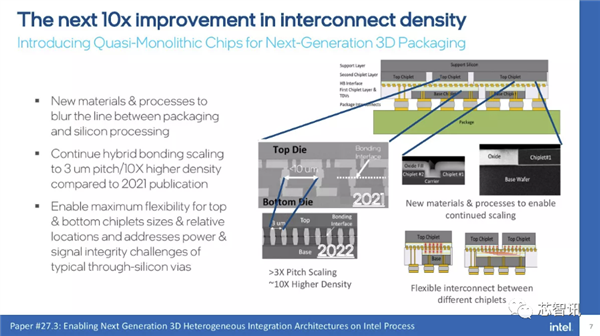

英特尔组件研究团队所研发的新材料和工艺模糊了封装和芯片制造之间的界限。

英特尔展示了将摩尔定律推进到在单个封装中集成一万亿个晶体管的关键步骤,包括可将互联密度再提升10倍的先进封装技术,实现了准单片(quasi-monolithic)芯片。

英特尔还通过材料创新找到了可行的设计选择,使用厚度仅三个原子的新型材料,从而超越RibbonFET,推动晶体管尺寸的进一步缩小。

英特尔通过下一代3D封装技术实现准单片芯片:

与IEDM 2021上公布的成果相比,英特尔在IEDM 2022上展示的最新混合键合研究将功率密度和性能又提升了10倍。

通过混合键合技术将互连间距继续微缩到3微米(去年还是10微米,现在缩小了超过3倍),英特尔实现了与单片式系统级芯片(system-on-chip)连接相似的互连密度和带宽(相比去年论文提到的互联密度提升了10倍)。此外,混合键合技术还支持多个小芯片直堆叠。

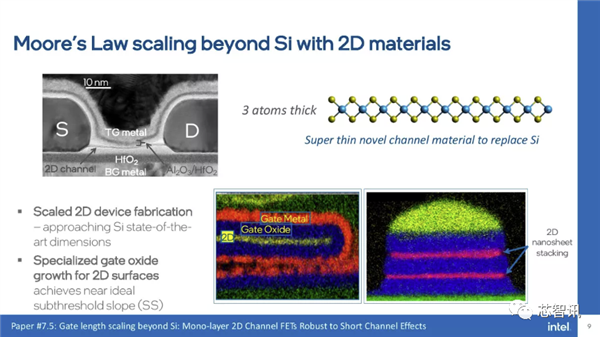

英特尔探索通过超薄“2D”材料,在单个芯片上集成更多晶体管:

英特尔展示了一种全环绕栅极堆叠式纳米片结构,使用了厚度仅3个原子的2D通道材料,同时在室温下实现了近似理想的低漏电流双栅极结构晶体管开关。这是堆叠GAA晶体管和超越硅材料的固有限制所需的两项关键性突破。

目前的芯片材料,如硅,是由三维晶体组成,这意味着原子在所有三个维度上都键合在一起,因此对微缩提出了基本的限制。相比之下,2D材料很有吸引力,因为所有原子都粘在一个平面上。

目前的GAA设计由堆叠的水平硅纳米片组成,每个纳米片完全被一个门包围。

这种“环绕栅极”(GAA)技术可减少电压泄漏,从而防止关闭晶体管。随着晶体管的缩小,这正变得越来越成为一个问题——即栅极在三面环绕沟道时,正如我们在鳍式场效应晶体管中看到的那样。

英特尔将其 GAA 设计命名为 RibbonFET,计划于 2024 年上半年量产。然而,超越RibbonFET将需要进一步的创新,而这项2D材料研究符合潜在创新要求。

英特尔的论文描述了一种新的环绕栅极(GAA)堆叠纳米片结构,其通道材料(纳米片/纳米带)采用的是厚度仅为3个原子的2D材料,可以在室温下以低泄漏电流工作。

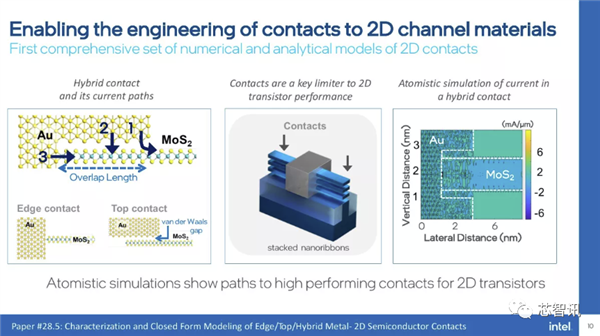

2D 通道材料的薄型使得建立与纳米带的电气连接成为一项艰巨的任务,因此英特尔的研究人员还展示了对2D材料的电接触拓扑结构(electrical contact topologies)的首次全面分析,为打造高性能、可扩展的晶体管通道进一步铺平道路。

为了实现更高性能的计算,英特尔带来了能效和存储的新可能:

通过开发可垂直放置在晶体管上方的存储器,英特尔重新定义了微缩技术,从而更有效地利用芯片面积。

英特尔在业内率先展示了性能可媲美传统铁电沟槽电容器(ferroelectric trench capacitors)的3D堆叠型铁电电容器(stacked ferroelectric capacitors),可用于在逻辑芯片上构建铁电存储器(FeRAM)。

这项技术最令人印象深刻的方面是,铁电沟槽电容器可以垂直堆叠在晶体管顶部的逻辑芯片上。

这使得存储器能够分层在逻辑元件之上,而不是像我们在其他类型的嵌入式存储器中看到的那样,如用于L1和L2缓存的SRAM,位于其自己的独特区域。

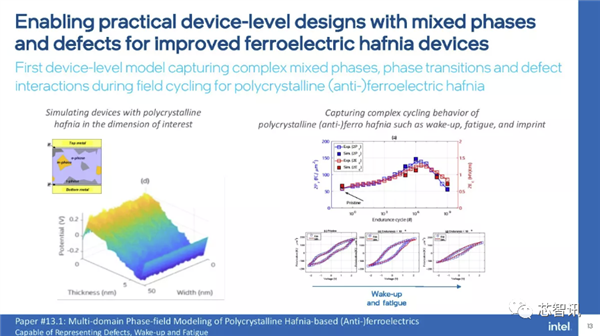

这种业界首创的器件级模型,可定位铁电氧化器件(ferroelectric hafnia devices)的混合相位和缺陷,标志着英特尔在支持行业工具以开发新型存储器和铁电晶体管方面取得了重大进展。

铁电存储器还具有与NAND闪存类似的功能,即在通常仅存储1bit的结构中存储多bit数据的能力。

在这种情况下,英特尔展示了每个沟槽存储4bit的能力。当然,这种方法将增加带宽和内存密度,同时减少延迟,产生更大、更快的片上缓存。

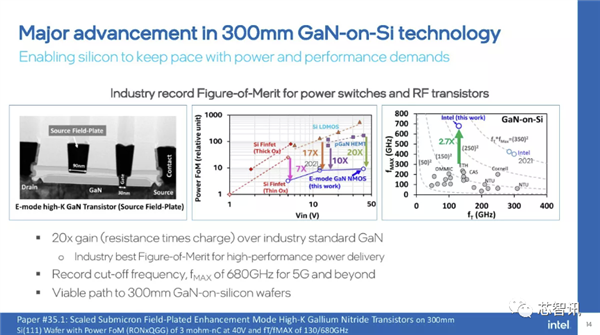

英特尔正在为打造300毫米硅基氮化镓晶圆(GaN-on-silicon wafers)开辟一条可行的路径,从而让世界离超越5G和电源能效问题的解决更进一步。英特尔在这一领域所取得的突破,实现了比行业标准高20倍的增益,并在高性能供电指标上打破了行业记录。

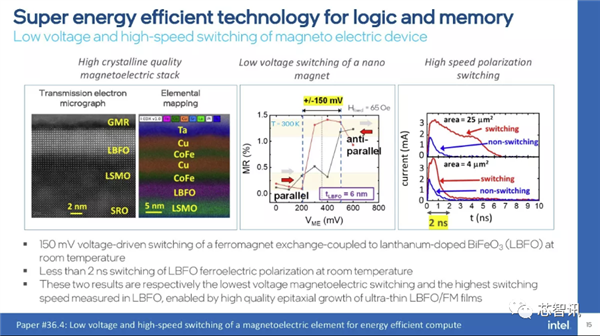

英特尔正在超高能效技术上取得突破,特别是在断电情况下也能保留数据的晶体管。对于三个阻碍该技术在室温下完全实现并投入使用的障碍,英特尔的研究人员已经解决其中两个。

英特尔继续引入新的物理学概念,制造用于量子计算的性能更强的量子位:

英特尔的研究人员加深了对各种界面缺陷(interface defects)的认识,这些缺陷可能会成为影响量子数据的环境干扰(environmental disturbances),从而找到了储存量子信息的更好方法。

Intel 18A提前到2024下半年量产

据英特尔最新对外公布的信息显示,Intel 4nm芯片已准备投产,它将用于包括Meteor Lake(14代酷睿流星湖)处理器、ASIC网络产品等。

同时,Intel 3nm、20A(2nm,其中A代表埃米,1nm=10埃米,下同)、18A(1.8nm)进展一切顺利,甚至还略有提前。

其中Intel 3nm将在明年下半年投产,用于Granite Rapids和Sierra Forest数据中心产品。

Intel 20A计划2024上半年准备投产,首发Arrow Lake(15代酷睿)客户端处理器,Intel 18A提前到2024下半年就绪,分别用在下一代酷睿和数据中心产品上。

纳米技术怎样制作纳米芯片?

2002年7月份,曾在几年前宣布摩尔定律死刑的这一定律的创始人戈登·摩尔接受了记者的采访。不过,这次他表现得很乐观,他表示:“芯片上晶体管数量每18个月增加二倍的速度虽然目前呈下降趋势,但随着纳米技术的发展,未来摩尔定律依然会继续生效。”看来,摩尔本人也把希望放到了纳米技术上。下面就让我们来看看纳米技术怎样制造纳米芯片。

我们知道目前的计算机芯片是用半导体材料做的。20世纪可以说是半导体的世纪,也可以说是微电子的世纪,微电子技术是指在半导体单晶材料(目前主要是硅单晶)薄片上,利用微米和亚微米精细结构技术,研制由成千上万个晶体管和电子元件构成的微缩电子电路(称为芯片),并由不同功能的芯片组装成各种微电子仪器、仪表和计算机。芯片可以看做是集成电路块。集成电路块从小规模向大规模发展的历程,可以看做是一个不断向微型化发展的过程。20世纪50年代末发展起来的小规模集成电路,集成度(一个芯片包含的元件数)为10个元件;20世纪60年代发展成中规模集成电路,集成度为1000个元件;20世纪70年代又发展了大规模集成电路,集成度达到10万个元件;20世纪肋年代更发展了特大规模集成电路,集成度超过100万个元件。1988年,美国国际商用机器公司(1BM)已研制成功存储容量达64兆的动态随机存储器,集成电路的条宽只有0.35微米。目前实验室研制的新产品为0.25微米,并向0.1微米进军。到2001年已降到0.1微米,即100纳米。这是电子技术史上的第四次重大突破。今天,芯片的集成度已进一步提高到1000万个元件。集成电路的条宽再缩小,将出现一系列物理效应,从而限制了微电子技术的发展。为了解决这个挑战,已经提出纳米电子学的概念。这一现象说明了:随着集成电路集成度的提高,芯片中条宽越来越小,因此对制作集成电路的单晶硅材料的质量要求越来越高,哪怕是一粒灰尘也可能毁掉一个甚至几个晶体管,这也是为什么摩尔本人几年前宣判摩尔定律“死刑”的原因。

据有关专家预测,在21世纪,人类将开发出徽处理芯片与活细胞相结合的电脑。这种电脑的核心元件就是纳米芯片。芯片是电脑的关键器件。生命科学和材料科学的发展,科学家们正在开发生物芯片,包括蛋白质芯片及DNA芯片。

蛋白质芯片,是用蛋白质分子等生物材料,通过特殊的工艺制备成超薄膜组织的积层结构。例如把蛋白质制备成适当浓度的液体,使之在水面展开成单分子层膜,再将其放在石英层上,以同样方法再制备——层有机薄膜,即可得到80~480纳米厚的生物薄膜。这种薄膜由两种有机物薄膜组成。当一种薄膜受紫外光照射时,电阻上升约40%左右,而用可见光照射时,又恢复原状。而另一种薄膜则不受可见光影响,但它受到紫外光照射时,电阻便减少6%左右。据介绍,日本三菱电机公司把两种生物材料组合在一起,制成了可以光控的新型开关器件。这种薄膜为进一步开发生物电子元件奠定了实验基础,并创造了良好的条件。

这种蛋白质芯片,体积小、元件密度高,据测每平方厘米,可达1015~1016个,比硅芯片集成电路高上万倍,表明这种芯片制成的装置其运行速度要比目前的集成电路快得多。由于这种芯片是由蛋白质分子组成的,在一定程度上具有自我修复能力,即成为一部活体机器,因此可以直接与生物体结合,如与大脑、神经系统有机地连接起来,可以扩展脑的延伸。有人设想,将蛋白质芯片植入大脑,将会出现奇迹。如视觉先天缺陷或后天损伤可以得到修复,使之重现光明等。

虽然目前生产与装配上述分子元件还处于探索阶段,而且天然蛋白质等生物材料不能直接成为分子元件,必须在分子水平上进行加工处理,这有很大难度,但前途是光明的。据介绍,日本已制定了开发生物芯片的10年计划,政府计划投入100亿日元做各项研究。世界上一些大公司,如日立、夏普等都看好生物芯片的前景,十分重视这项研究工作。

人的大脑约有140亿个神经细胞,掌管着思维、感觉及全身的活动。虽然电脑已面世多年;但其精细程度和人脑相比,仍然差一大截。为了使电脑早日具有人脑的功能和效率,科学家近年致力研究开发人工智能电脑,并已取得不少进展。人工智能电脑是以生物芯片为基础的。生物芯片有多种,血红蛋白集成电路就是新型的生物芯片之一。

美国生物化学家詹姆士·麦克阿瑟,首先构想把生物技术与电子技术结合起来。他根据电脑的二进制工作原理,发现血红蛋白也具有类似“开”和“关”的双稳态特性。当改变血红蛋白携带的电荷时,它会出现上述两种变化,这就有可能利用生物的血红蛋白构成像硅电子电路那样的逻辑电路。麦克阿瑟首先利用生物工程的重组DNA技术,制成了血红蛋白“生物集成电路”,使研制“人造脑袋”取得了突破性进展。此后,生物集成电路的研究便逐步展开。美国科学家在硅晶片上重组活细胞组织获得成功。它具有硅晶片的强度,又有生物分子活细胞那样的灵活和智能。德国科学家所研制成的聚赖氨酸立体生物晶片,在1立方毫米晶片上可含100亿个数据点,运算速度更达到10皮秒(一千亿分之一秒),比现有的电脑快近100万倍。

DNA芯片又称基因芯片,DNA是人类的生命遗传物质脱氧核糖核酸的简称。因为DNA分子链是以ATGC(A-T、G-C)为配对原则的,它采用一种叫做“在位组合合成化学”和微电子芯片的光刻技术或者用其他方法,将大量特定顺序的稤NA片段,有序地固化在玻璃或者硅片上,从而构成储存有大量生命信息的DNA芯片。DNA芯片,是近年来在高新科技领域出现的具有时代特征的重大技术创新。

每一个DNA就是一个微处理器。DNA计算速度是超高速的,理论上计算,它的运算速度每小时可达1015次数,是硅芯片运算速度的1000倍。而且,DNA的存储量是很大的,每克DNA可以储存上亿个光盘的信息。不过,目前的主要难点是解决DNA的数据输出问题。

DNA芯片有可能将人类的全部约8万个基因集约化地固定在1平方厘米的芯片上。在与待测样品的DNA配对后,DNA芯片即可检测出大量相应的生命信息。例如寻找基因与癌症、传染病、常见病和遗传疾病的关系,进一步研究相应药物。目前已知有6000多种遗传病与基因相关,还有环境对人体的影响,例如花粉过敏和对环境污染的反应等都与基因有关。已知有200多个与环境影响相关的基因,对这些基因的全面监测,对生态、环境控制及人类健康均有重要意义。

DNA芯片技术既是人类基因组研究的重要应用课题,又是功能基因研究的崭新手段。例如单核苷酸的多态性,是非常重要的生命现象,科学家认为,人体的多样性和个性取决于基因的差异,正是这种单核苷酸多态性的表现,如人的体形、长相与500多个基因相关。通过DNA芯片,原则上可以断定人的特征,甚至脸形、长相、外貌特点,生长发育差异等。

“芯片巨人”英特尔公司于2000年12月公布,英特尔公司用最新纳米技术研制成功30纳米晶体管芯片。这一突破将使电脑芯片速度在今后5~10年内提高到2000年的10倍,同时使硅芯片技术向物理极限更近一步。新型芯片的运算速度已达目前运算速度最快芯片的7倍。它能在子弹飞行30厘米的时间内运算2000万次,或在子弹飞行25毫米的时间内运算200万次。晶体管门是计算机芯片进行运算的开关,新芯片是以3个原子厚度的晶体管“门”为基础,比目前计算机使用的180纳米晶体管薄很多。要制造这种芯片的障碍是控制它产生的热量。芯片的运行速度越快,产生的热量就越多。过多的热量会使制造计算机芯片所用的材料受到损坏。英特尔公司经过了长期的研究,解决了这一问题。这种原子级晶体管是用新的化学合成物制成的,这种新材料可以使芯片在运行时温度不会过高。这种芯片的出现将为研制模拟以人的方式,可以和人进行交流的电脑创造条件。英特尔公司说,他们开发出的这种迄今世界上最小最快的晶体管,厚度仅为30纳米。这将使英特尔公司可以在未来5~10年内生产出集成有4亿个晶体管、运行速度为每秒10亿次,工作电压在1伏以下的新型芯片。而目前市场上出售的速度最快的芯片“奔腾4代”集成了4200万个晶体管。英特尔公司称,用这种新处理器制造的产品最早将在2005年以后投放市场。

英特尔公司的一位工程师说:“30纳米晶体管的研制成功使我们对硅的物理极限有了新看法。硅也许还可以使用15年,此后会有什么材料取代硅,那是谁也说不准的事。”他又说:“更小的晶体管意味着更快的速度,而运行速度更快的晶体管是构筑高速电脑芯片的核心模块,电脑芯片则是电脑的‘大脑’。”英特尔公司预测,利用30纳米晶体管设计出的电脑芯片可以使“万能翻译器”成为现实。比如说英语的人到中国旅游,就可以通过随身携带的翻译器,将英语实时翻译成中文,在机场、旅馆或商店不会有语言障碍。在安全设施方面,这种芯片可以使警报系统识别人的面孔。此外,将来用几千元人民币就可以买一台高速台式电脑,其运算能力可以跟现在价值上千万元的大型主机媲美。

单位面积上晶体管的个数是电脑芯片集成度的标志,晶体管数量越多,说明集成度越高,而集成度越高,处理速度就越快。30纳米晶体管将开始出现在用0.07微米技术产品上,目前英特尔公司使用的是0.18微米技术,而1993年的“奔腾”处理器使用的是0.35微米技术。在芯片上“刻画”电路,0.07微米技术用的是超紫外线光刻技术,比2001年最先进的深紫外线光刻技术更为先进。如果在纸上画线,深紫外线光刻使用的是钝铅笔,而超紫外线光刻使用的是削尖了的铅笔。

晶体管越来越小的好处主要有两方面:一是可以用较低,的成本提高现有产品性能;二是工程师可以设计原来不可能的新产品。这两个好处正是推动半导体技术发展的动力,因为企业提高了利润,就有可能在研发上投入更多。看来,纳米技术的确可以延长摩尔定律的寿命,这也正是摩尔本人和众多技术人员把目光放到纳米技术之上的原因所在。

什么是45纳米制程技术?

概述:英特尔45纳米高K半导体制程技术全称为英特尔45纳米高K金属栅硅制程技术。该技术突破性的采用金属铪制作具有高K特性的栅极绝缘层,是半导体行业近40年来的重要创新。英特尔的65纳米制程升级为45纳米制程技术并非以往升级所带来的量变,而是脱胎换骨的飞跃。凭借制程的创新,英特尔迈出TICK-TOCK产品发展战略稳健的又一步,并拉开了半导体行业发展的历史新篇章。这一创新再次延续了摩尔定律,使之在未来10年继续有效。 随着英特尔45纳米半导体制程技术揭开神秘面纱,一系列采用该技术的服务器、工作站及台式机处理器同期发布。较前代产品,新产品在性能、能耗比以及经济性方面有显著提高,并将在正式发布后向市场供货。 预览英特尔45纳米制程技术创新 英特尔45纳米高k金属栅极晶体管技术 英特尔45纳米高k金属栅极晶体管技术是英特尔制造晶体管的新方法,它以一种具有高k特性的新材料作为“栅极电介质”,并采用了一种新型金属材料作为晶体管的“栅极”。向这些新材料组合的转变,标志着40多年来晶体管制造方式最重大的变革。 采用英特尔45纳米高k晶体管的优势 全新英特尔45纳米高k晶体管方案通过缩小晶体管的体积解决了漏电率问题。它能降低晶体管的漏电率,帮助英特尔的工程师们在提供更高性能的同时降低处理器的能耗。同时,笔记本电脑用户也将发现,漏电率的降低使得能耗也随之减少,电池的使用时间更长了。 英特尔在新制程技术中采用的新材料 高k材料基于一种名为铪的元素,而不是以往的二氧化硅;而晶体管栅极则由两种金属元素组成,取代了硅。多数晶体管和芯片仍基于先进的英特尔硅制程技术制造。新的方案中结合了所有这些新材料,是英特尔提升处理器性能的独特手段。 采用金属铪的价值所在 铪是元素周期表中的72号元素,也是一种金属材料。它呈银灰色,具有很高的韧性和防腐性,化学特性类似于锆。英特尔之所以在45纳米晶体管中采用铪来代替二氧化硅,是因为铪是一种较厚(thicker)的材料,它能在显著降低漏电量的同时,保持高电容来实现晶体管的高性能。